计算机组成原理

一、计算机系统概述

1.1 硬件的发展

1946年,第一台电子数字计算机(ENIAC)诞生,采用电子管作为逻辑元件。体积超大,耗电量巨大,使用纸带机编程。

1958年,第二代计算机诞生,使用晶体管作为逻辑元件。

1964年,第三代计算机诞生,使用中小规模集成电路作为逻辑元件。

1972年,诞生了第四代计算机,使用大规模和超大规模集成电路作为逻辑元件。

微处理器的发展:

| 微处理器 | 机器字长 |

|---|---|

| 8080 | 8位 |

| 8086,80286 | 16位 |

| 80386,80486 | 32位 |

| Pentium(奔腾) | 64位 |

1.2 计算机硬件的组成

冯·诺依曼计算机的特点:

- 计算机由五大部件组成

- 指令和数据以同等地位存于存储器,可按地址寻访

- 指令和数据用二进制表示

- 指令由操作码和地址码组成

- 存储程序

- 以运算器为中心

现代计算机以存储器为核心

对于主存储器,有三部分构成:

- 存储体

- 存储地址寄存器MAR

- 存储数据寄存器MDR

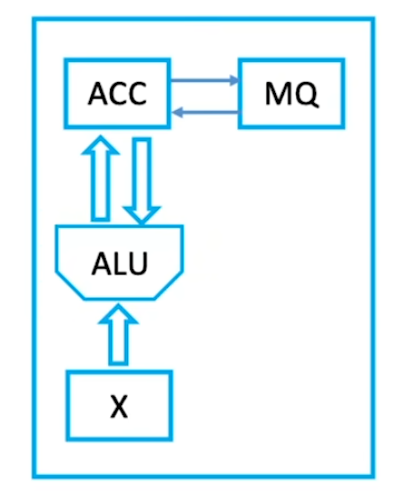

对于运算器,组成如下:

其中:

- ACC: 累加器,用于存放操作数,或运算结果。

- MQ: 乘商寄存器,在乘、除运算时,用于存放操作数或运算结果。

- X: 通用的操作数寄存器,用于存放操作数。

- ALU: 算术逻辑单元,通过内部复杂的电路实现算数运算、逻辑运算。

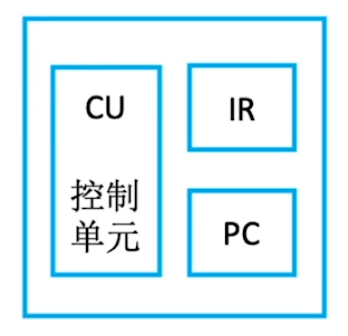

对于控制器,组成如下:

其中:

- CU: 控制单元,分析指令,给出控制信号

- IR: 指令寄存器,存放当前执行的指令

- PC: 程序计数器,存放下一条指令地址,有自动加1功能

1.3 计算机的性能指标

CPI(Clock cycle Per Instruction): 执行一条指令所需的时钟周期数。

执行一条指令的耗时:CPI * CPU时钟周期。

IPS(Instructions Per Second): 每秒执行多少指令。

FLOPS: 每秒执行多少次浮点运算。

二、数据的表示和计算

2.1 进位计数制

基数:每个数码位所用到的不同符号的个数,r进制的基数为r。

任意进制-->十进制:使用位权计算。

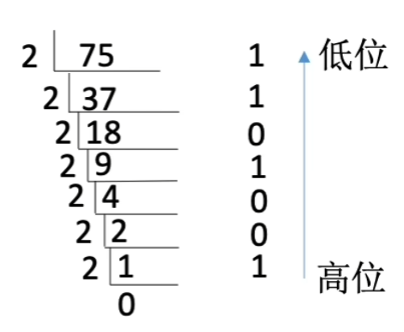

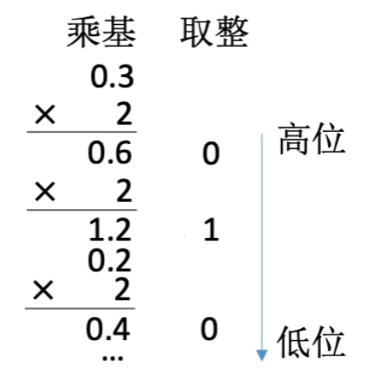

十进制-->任意进制:

整数部分:使用短除法

小数部分:

二进制-->八进制、十六进制:每3、4位一组,转换成对应的符号。

八进制、十六进制-->二进制:每个符号转换成对应的二进制串。

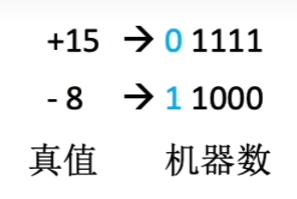

真值: 符合人类习惯的数字

机器数:数字实际存到机器里的形式,正负号需要被“数字化”

2.2 BCD码

BCD码(Binary-Coded Decimal),以一种符合人类习惯的编码方案。

- 8421码,即4个二进制串一组,位权分别为8421,遇到加法的时候,如果遇到了10~15,则加上6。

- 余3码,在8421码的基础上加上0b0011,每个位置的位权不固定,所以成为无权码。

- 2421码,类似8421码,只是位权不同。

2.3 无符号整数

- 全部二进制位都是数值位,没有符号位,第i位的位权是

- n 比特无符号整数表示范围

,超出则溢出,意味着该计算机无法一次处理这么多 - 可以表示的最小的数全0,可以表示的最大的数全1

无符号数加法:

- 计算机硬件如何做无符号整数的加法: 从最低位开始,按位相加,并往更高位进位

无符号数减法:

- 被减数不变,减数全部按位取反然后+1,这样减法就变成了加法。

- 从最低位开始,按位相加,并网更高位进位。

2.4 有符号整数

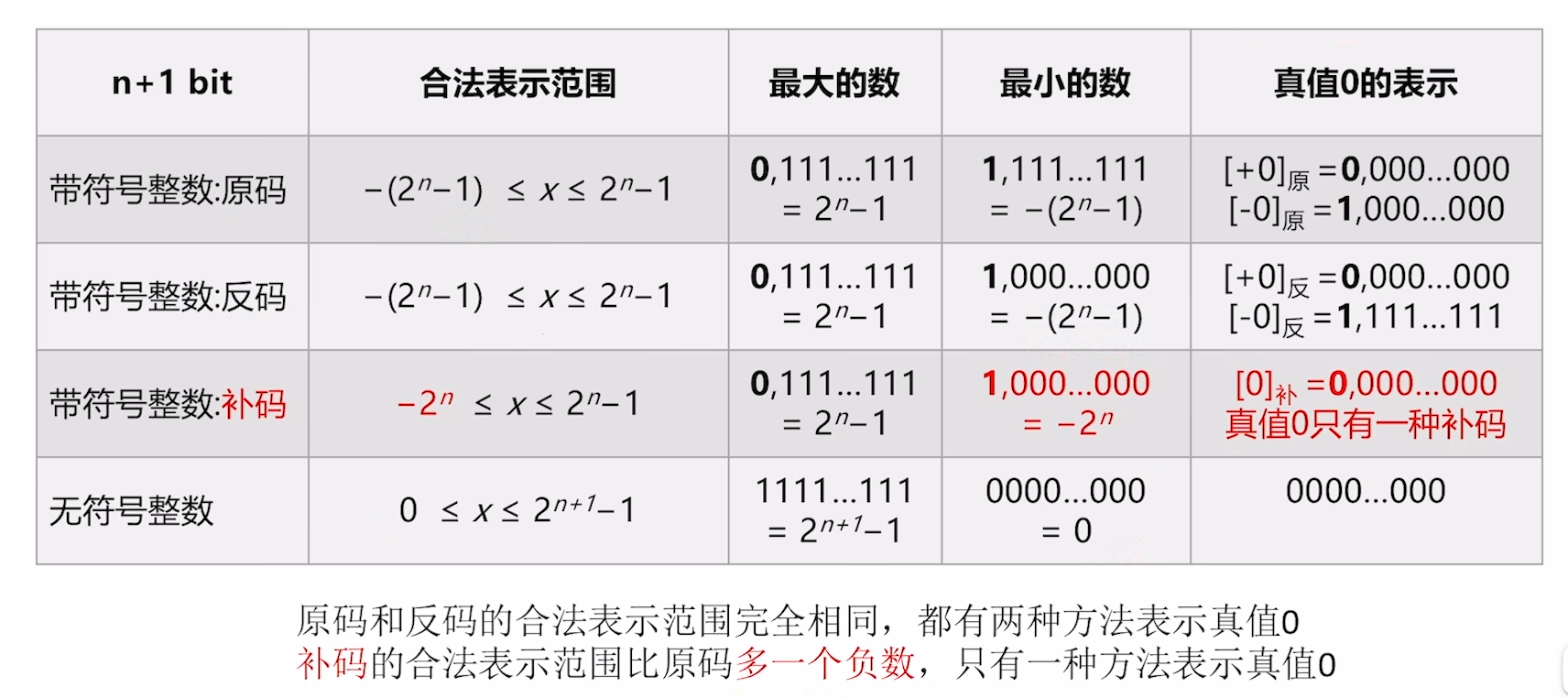

原码的缺点:符号位不能参与运算,需要设计复杂的硬件电路,因此诞生了补码。

对于正数:原码=补码=反码

对于负数:原码<-符号位不变,数值位取反->反码-->末尾+1-->补码

对于负数,原码和补码可以快速转换(双向):从右往左找到第一个1,这个1左边的所有数值位取反。

计算机硬件如何做补码的加法:

- 从最低位开始,按位相加(符号位参与运算),并往更高位进位

计算机硬件如何做补码的减法:

- [B]补<--全部位按位取反,末尾+1->[-B]补

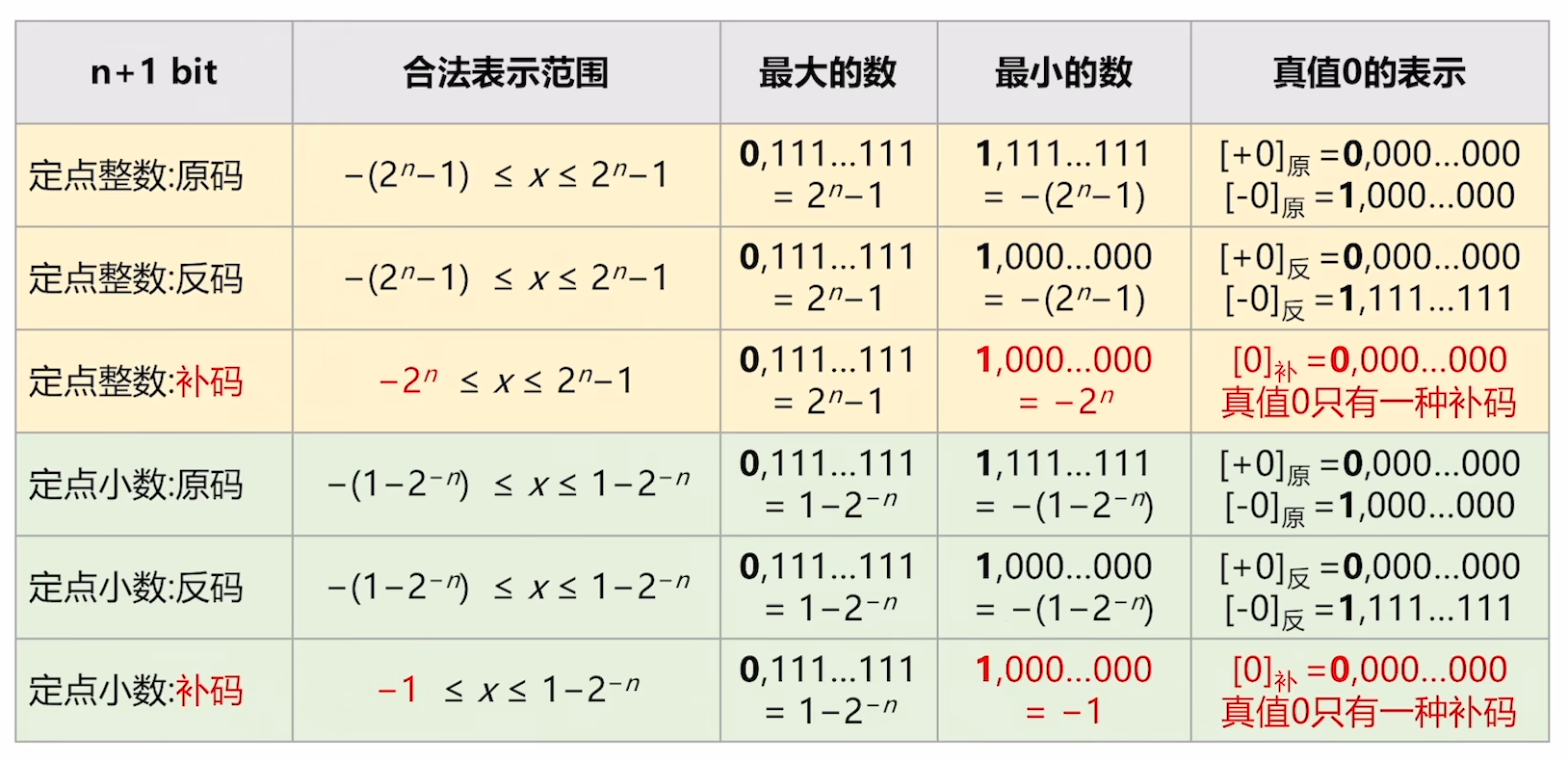

2.5 原码反码补码的特性

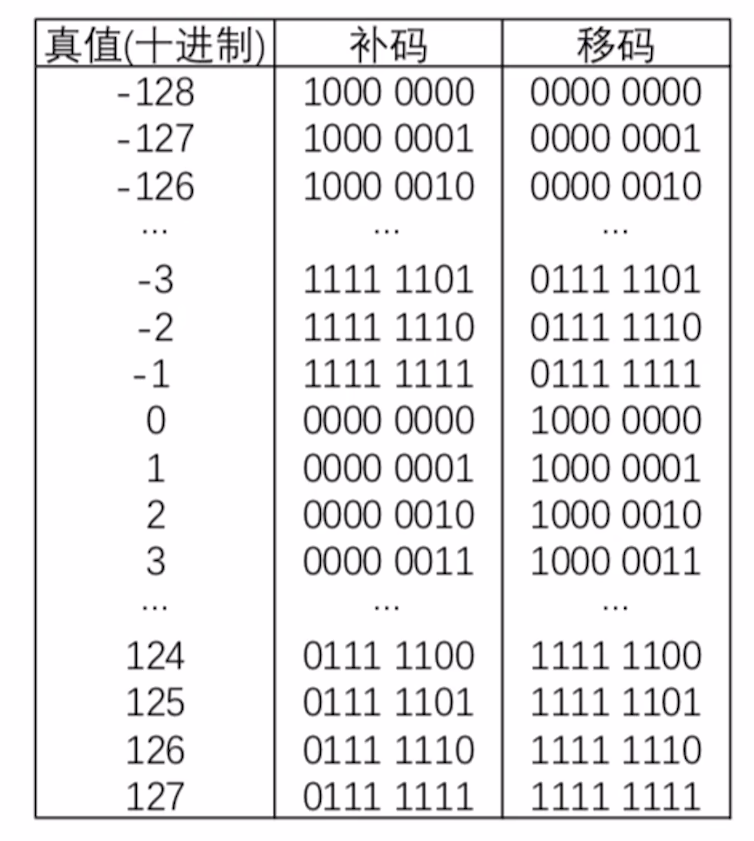

2.6 移码

移码:在补码的基础上,将符号位取反。注意,移码只能用于表示整数。

为什么要引入移码:用移码表示的整数可以很方便的利用硬件电路比较大小。

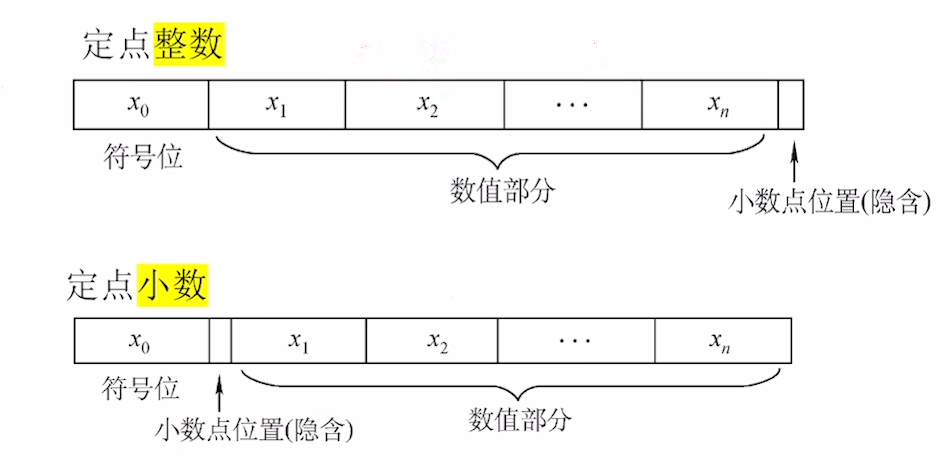

2.7 定点小数

定点数:小数点的位置固定

- 定点整数,即带符号整数

- 定点小数

定点小数的加法和减法参考定点整数,过程一模一样。

2.8 加法器设计

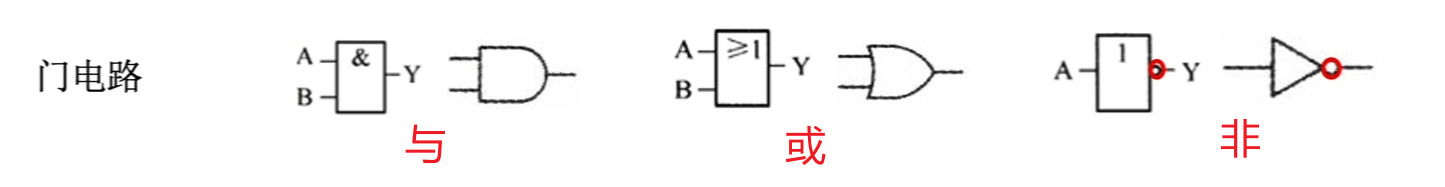

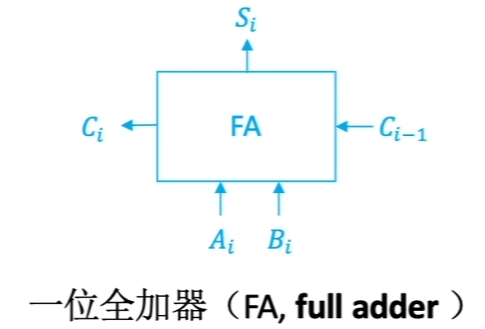

反演律又称为德摩根律

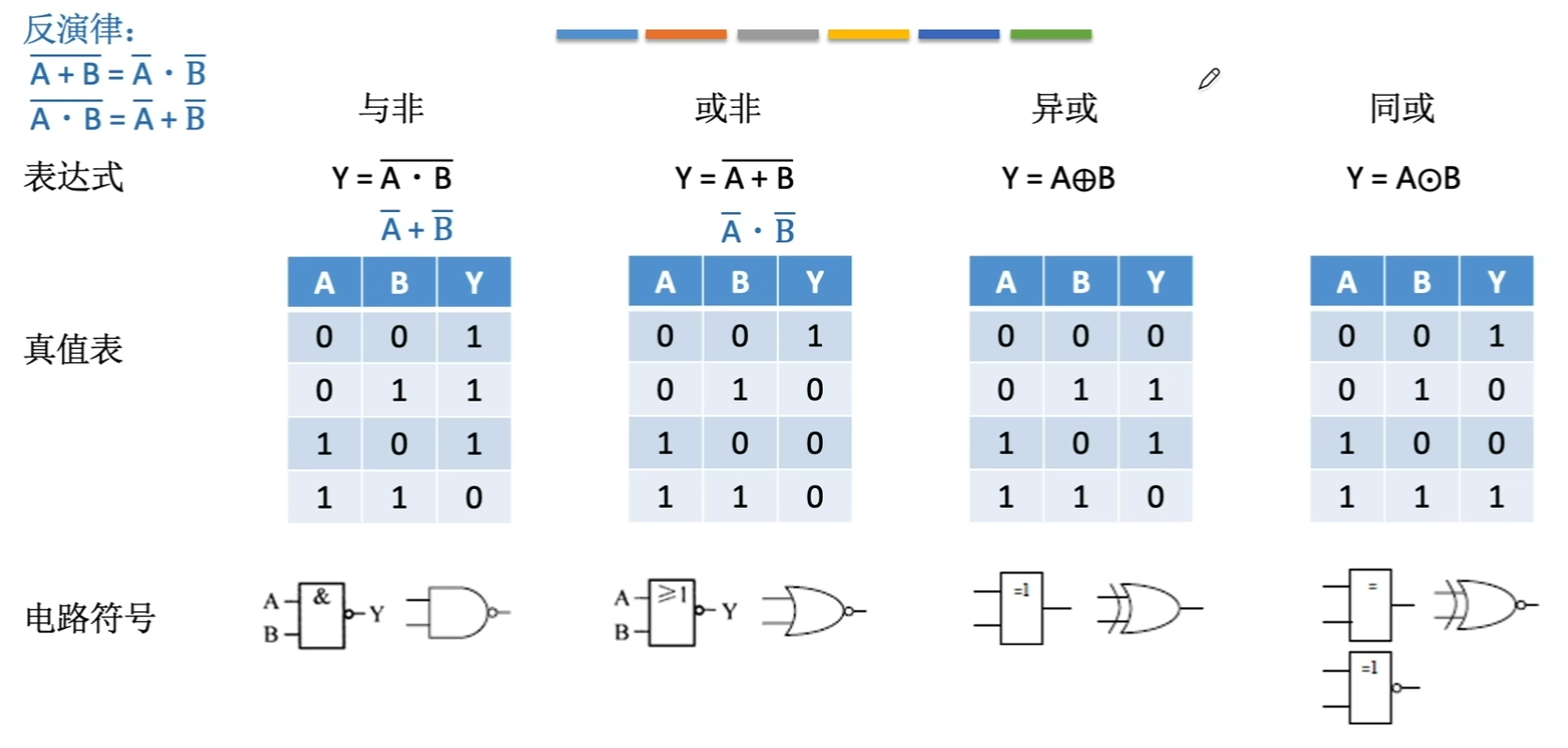

一位全加器:

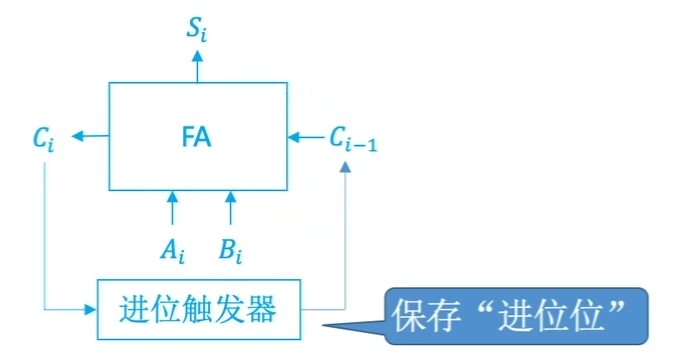

串形加法器:只有一个全加器,数据逐位串行送入加法器中进行算。进位触发器用来寄存进位信号,以便参与下一次运算。

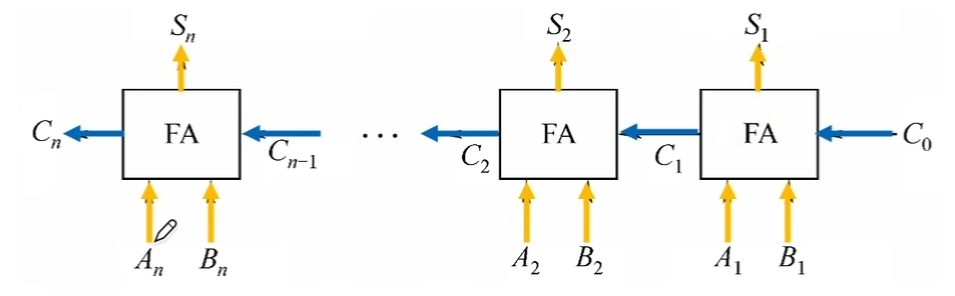

并行加法器:把n个全加器串联起来。又称行波进位,每一级的进位直接依赖于前一级的进位,即进位信号是逐级产生的。

并行进位的并行加法器。

即第i位向更高位的进位

但是一直套娃会造成电路越来越复杂,因此要适可而止,比如套娃到4位加法器,然后继续封装再套娃。

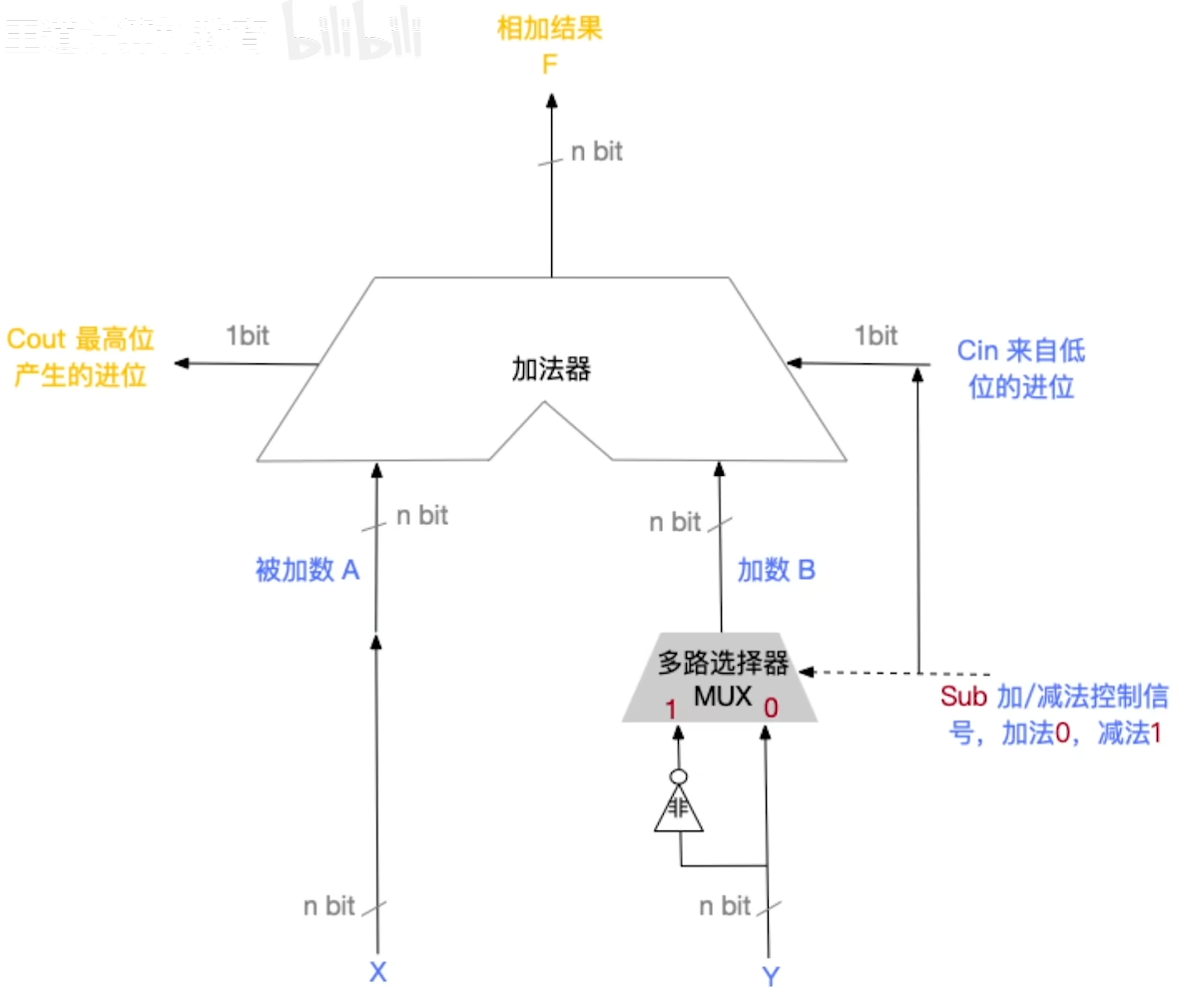

2.9 补码加减运算器

有符号数和无符号数的加法电路逻辑是相同的,只是溢出判断逻辑不同。

2.10 溢出判断

方法1:采用一位符号位

设A的符号为

若

方法2:采用一位符号位

设符号位进位为

方法3:采用双符号位

正数符号位为00,负数符号位为11。

设两个符号位为

双符号位补码又称:模4补码

单符号位补码又称:模2补码

符号拓展:

例如将数据从8位变成16位时

- 关于正数,原码反码补码的操作都是相同的,整数左添0,小数右添0

- 关于负数

- 整数:原码添0,反码补码添1

- 小数:原码添0,反码添1,补码添0

2.11 标志位生成

加法器除了输出结果,也会输出一些标志位。

- OF

- 含义:加减运算是否溢出,OF=1时溢出

- SF

- 含义:符号位,为0代表正数,反之负数

- ZF

- 含义:结果是否为0,ZF=1代表结果为0

- CF

- 含义:进位、借位标志,CF=1代表发生了进位或借位

说明:

- OF与SF只针对有符号数

- CF只针对无符号数(判断溢出)

2.12 移位运算

算数移位:

- 对于正数,则原码反码补码不管左移右移都是补0

- 对于负数

- 原码:左右移动都是补充0

- 反码:左右移动都是补充1

- 补码:左移补充0,右移补充1

逻辑移位:

- 逻辑左移和右移都是补充0。

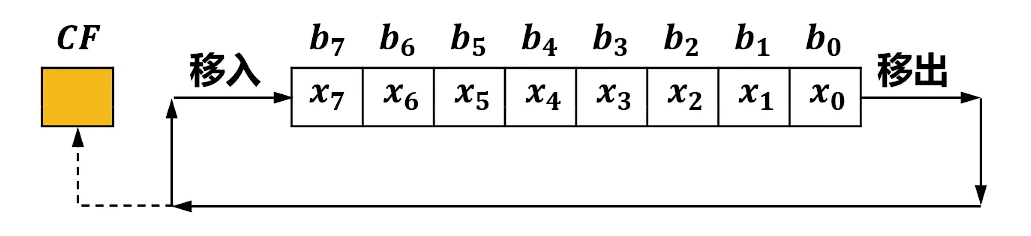

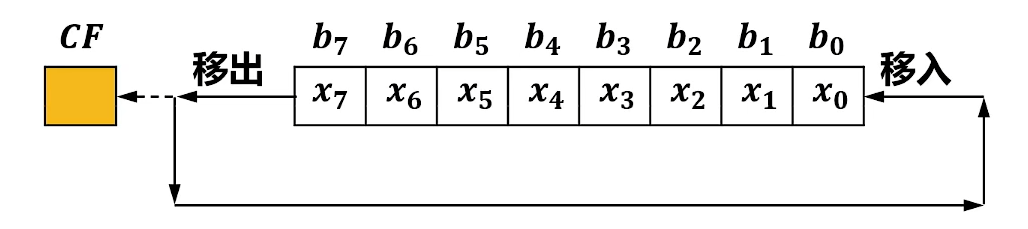

循环移位:

不带进位位

带进位位

2.13 数据的存储和排列

多字节在内存里一定是占连续的几个字节。

- 大端存储:最高有效字节(MSB)在低地址,最低有效字节(LSB)在高地址,便于人类阅读。

- 小端存储:与大端方式相反,便于机器处理。

边界对齐:

- 有的计算机每次访存只能读写一个字,因此需要边界对齐,不然就要增加访存次数。

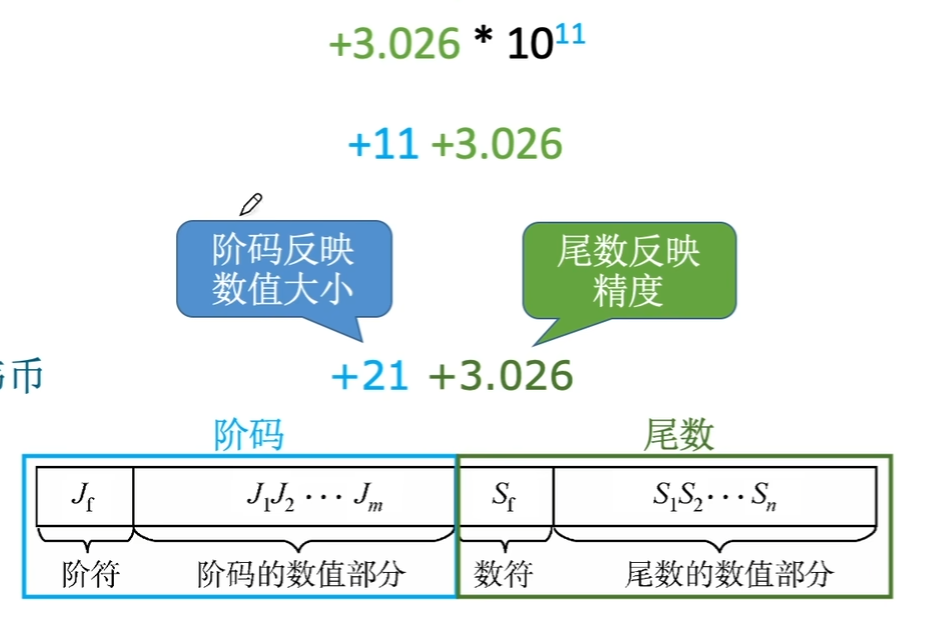

2.14 浮点数的表示

为什么要引入浮点数:定点数可表示的数字范围有限,但我们不能无限制的增加数据的长度。

浮点数尾数的规格化:尾数的最高位必须是有效位

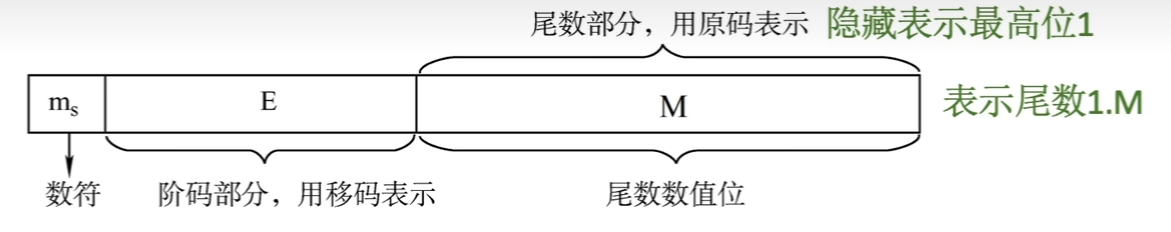

2.15 IEEE754

一般来说,移码=真值+偏置值(

但是在IEEE754中,偏置值为

| 类型 | 数符 | 阶码 | 尾数数值 | 总位数 | 偏置值 |

|---|---|---|---|---|---|

| 短浮点数 | 1 | 8 | 23 | 32 | 127 |

| 长浮点数 | 1 | 11 | 52 | 64 | 1023 |

三、存储系统

3.1 存储系统的基本概念

存储器的分类:

- 按照存储介质分类

- 以半导体器件存储信息,如主存,Cache

- 磁表面存储器,如磁盘、磁带

- 光存储器

- 按存取方式

- 随机存取存储器RAM

- 顺序存取存储器SAM,如磁带

- 直接存取存储器DAM,如磁盘,先直接存取,在按循序方式存取

- 相联存储器CAM,可以按照内容检索到存储位置,如快表TLB

- 按照信息的可保存性

- 断电后存储信息消失--易失性存储器,如主存

- 断电后依旧存储信息--非易失性存储器

- 读取后信息被破坏--破坏性读出--DRAM

- 读取后信息不被破坏--非破坏性读书--SRAM

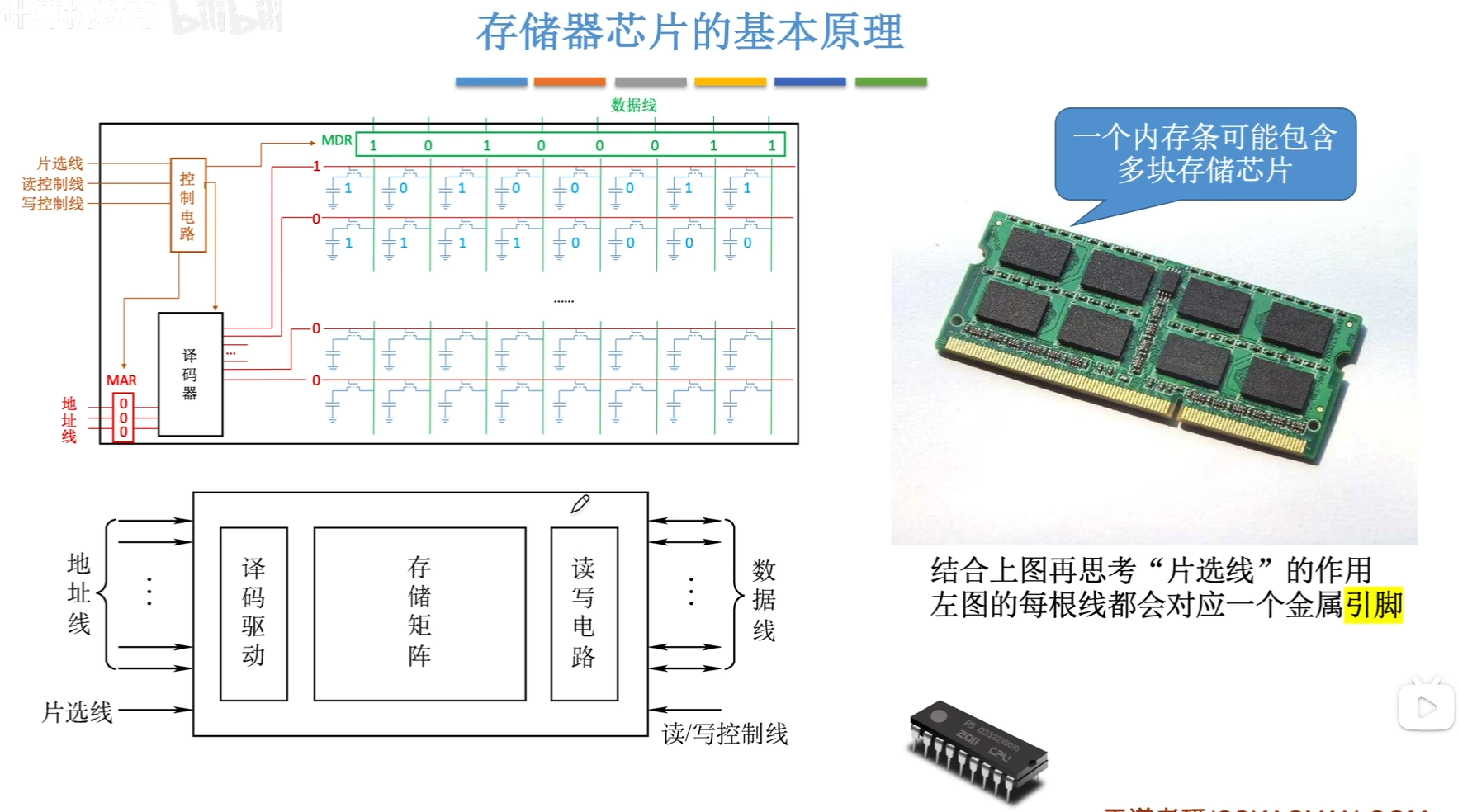

3.2 主存储器的基本组成

3.3 SRAM和DRAM

DRAM芯片:使用栅极电容存储信息,是破坏性读出,读后应该重写。集成度高,功耗低,成本低。

SRAM芯片:使用双稳态触发器存储信息,是非破坏性读出。成本高,集成度低,功耗高。

DRAM的刷新:

- 刷新周期大概2ms一次

- 每次刷新一行存储单元

- 如何刷新?有硬件支持,读出一行的信息后重新写入,占用一次读写周期。

- 在什么时刻刷新

- 分散刷新:刷新每次读写完刷新,系统存取周期变大

- 集中刷新:在2ms内安排时间集中刷新,有一段时间会无法访问存储器

- 异步刷新:在2ms每行刷新一次即可

注意,对于DRAM,行列地址是分成两次送的,即采用了地址线复用技术。而SRAM则是只需要一次。

目前DRAM已经过时,主存一般采用SDRAM,如DDR3,DDR4

3.4 ROM

- MROM:掩模式只读存储器。厂家写入信息。任何人不能重新写入,只能读取。

- PROM:可编程只读存储器,用户可用专门的PROM写入器写入信息,写一次后就不能更改。

- EPROM:可擦除可编程只读存储器。允许用户写入信息,并且允许多次擦除。

- UVEPROM:用紫外线擦除所有信息

- EEPROM:采用电擦除特定字

- Flash Memory:闪存,如U盘,SD卡。可进行多次快速擦除重写。每个存储元只需要单个MOS管,位密度比RAM高。由于闪存需要先擦除再写入,因此写比读慢

- SSD(Solid State Drives):固态硬盘,由控制单元+Flash芯片组成,与闪存的区别是控制单元。

事实上,主板上的ROM芯片(BIOS)也是主存的一部分,也会与RAM一起进行编址。

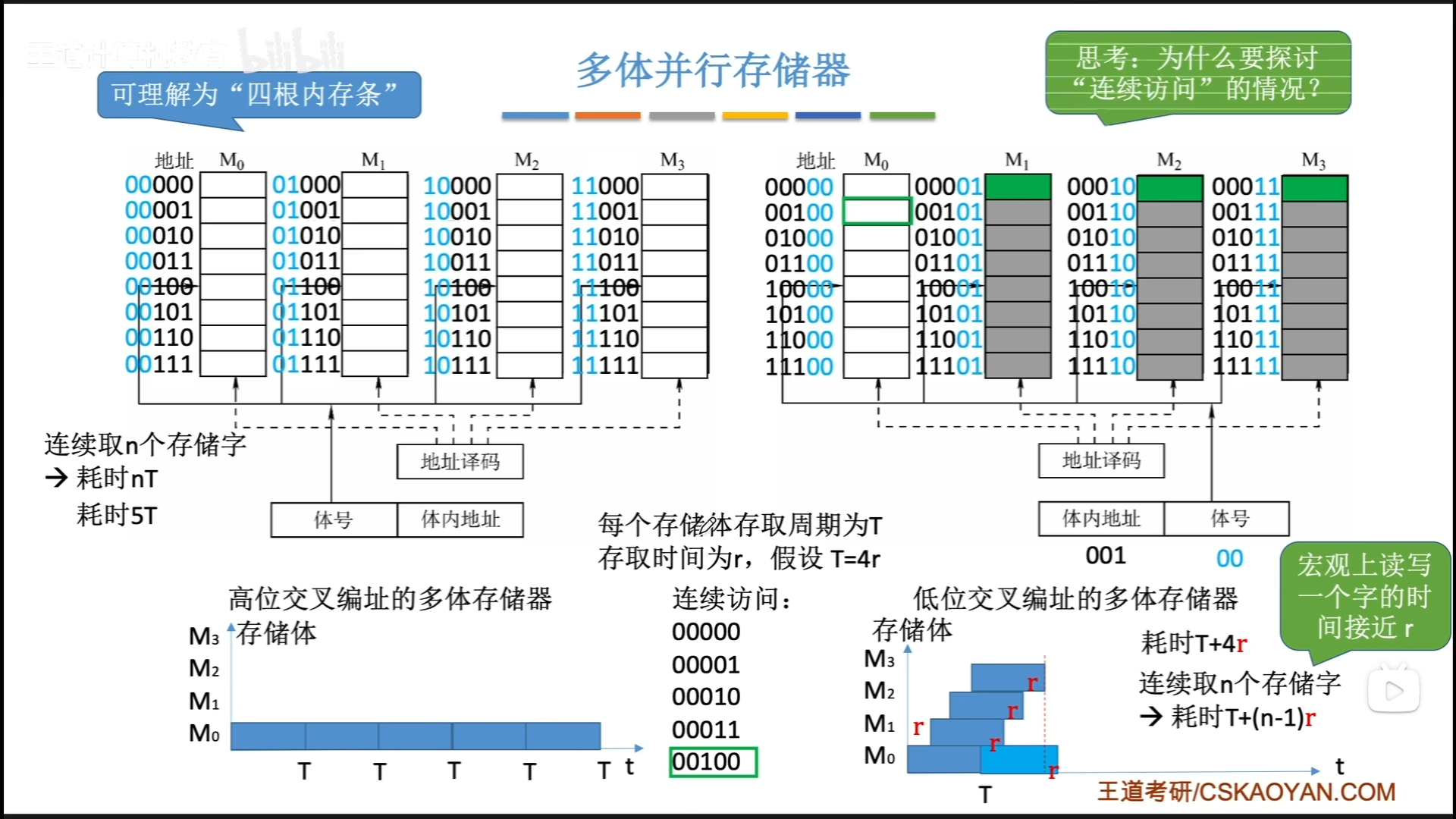

3.5 双端口RAM以及多模块存储

双端口RAM:

- 支持两个CPU同时访问RAM

- 若发生冲突,则发出BUSY信号,其中一个访问端口暂时关闭

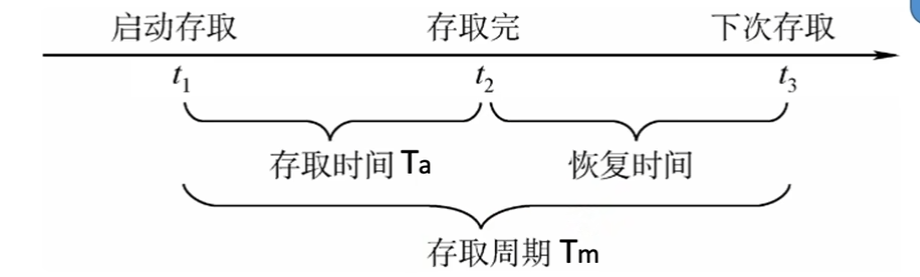

设存取周期为T,存取时间为r,为了使流水线不间断,则应保证模块数

除了多体并行,还可以单体多字,相当于位拓展,但是灵活性不高

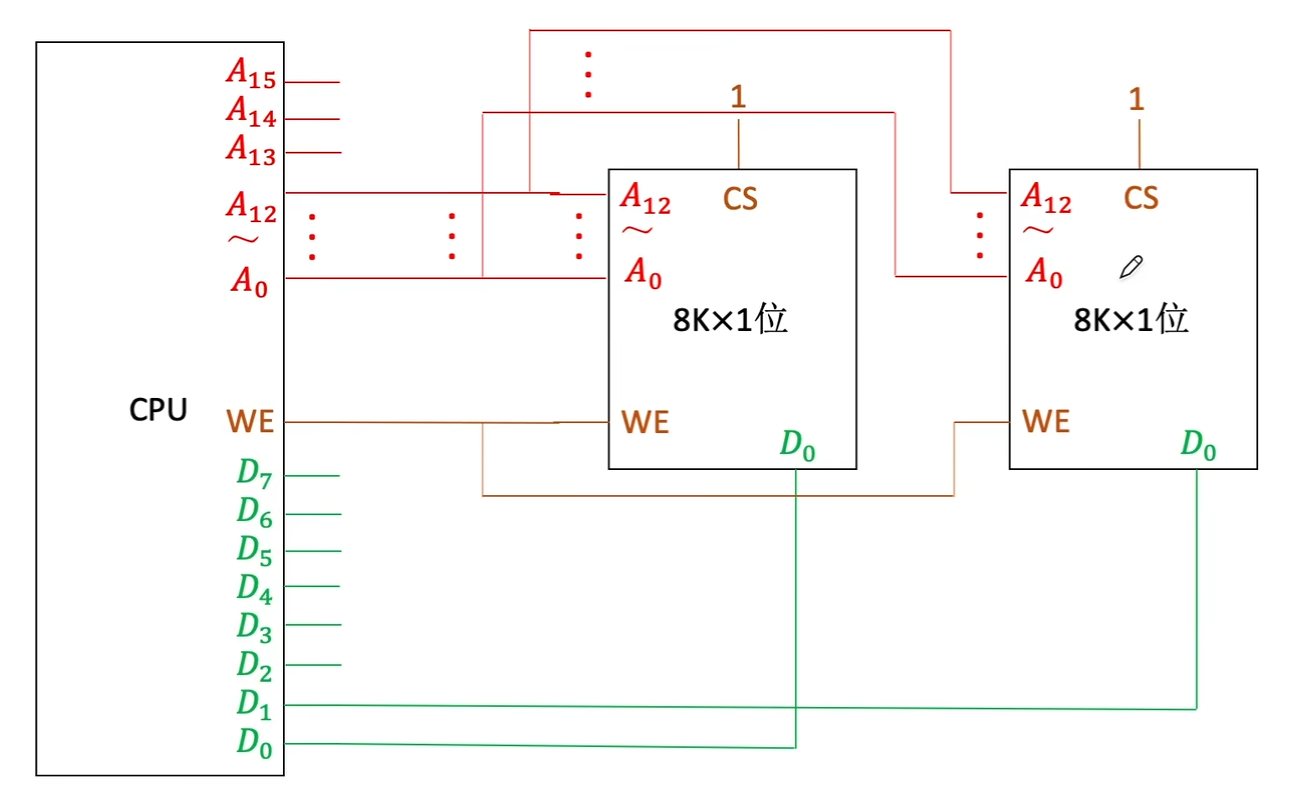

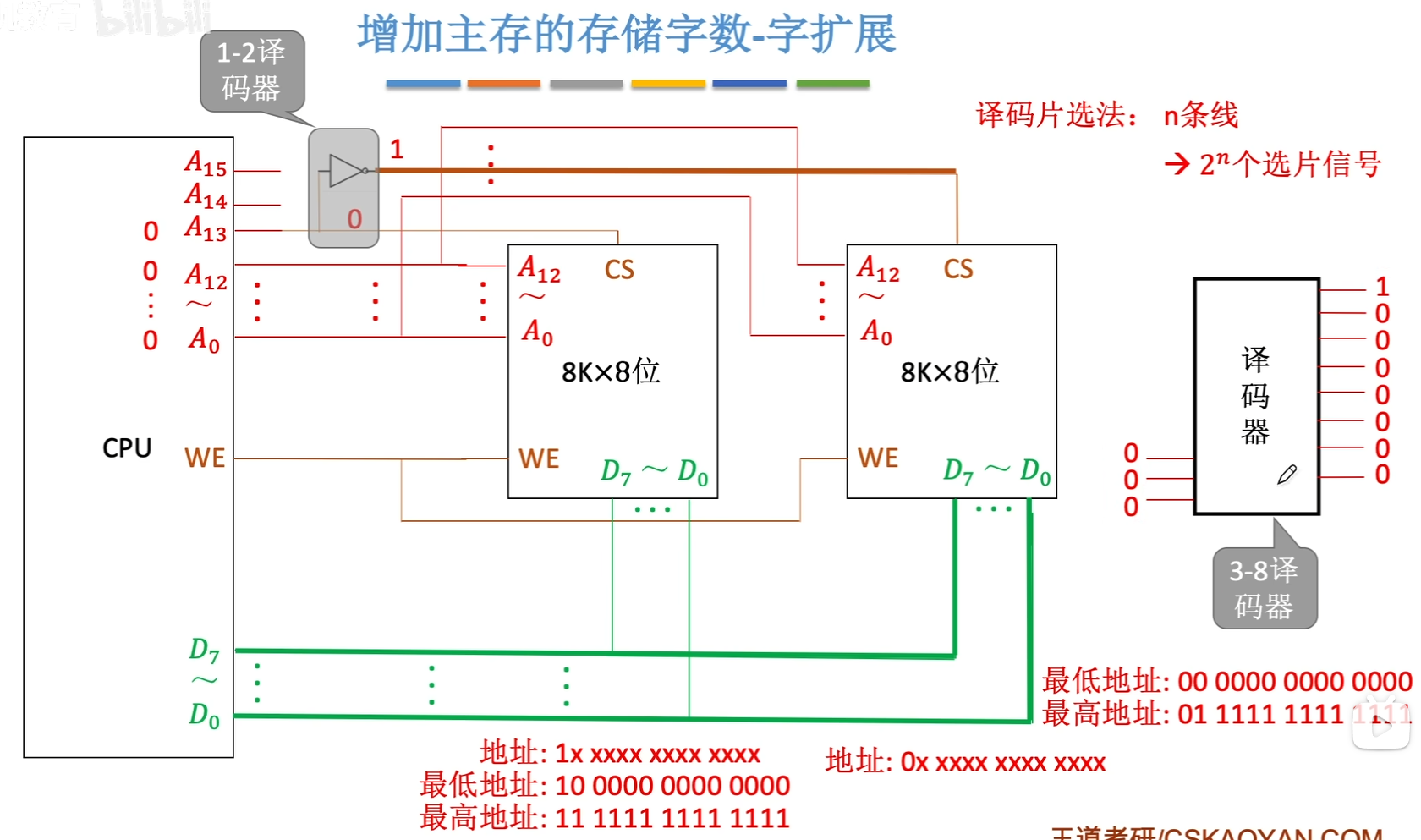

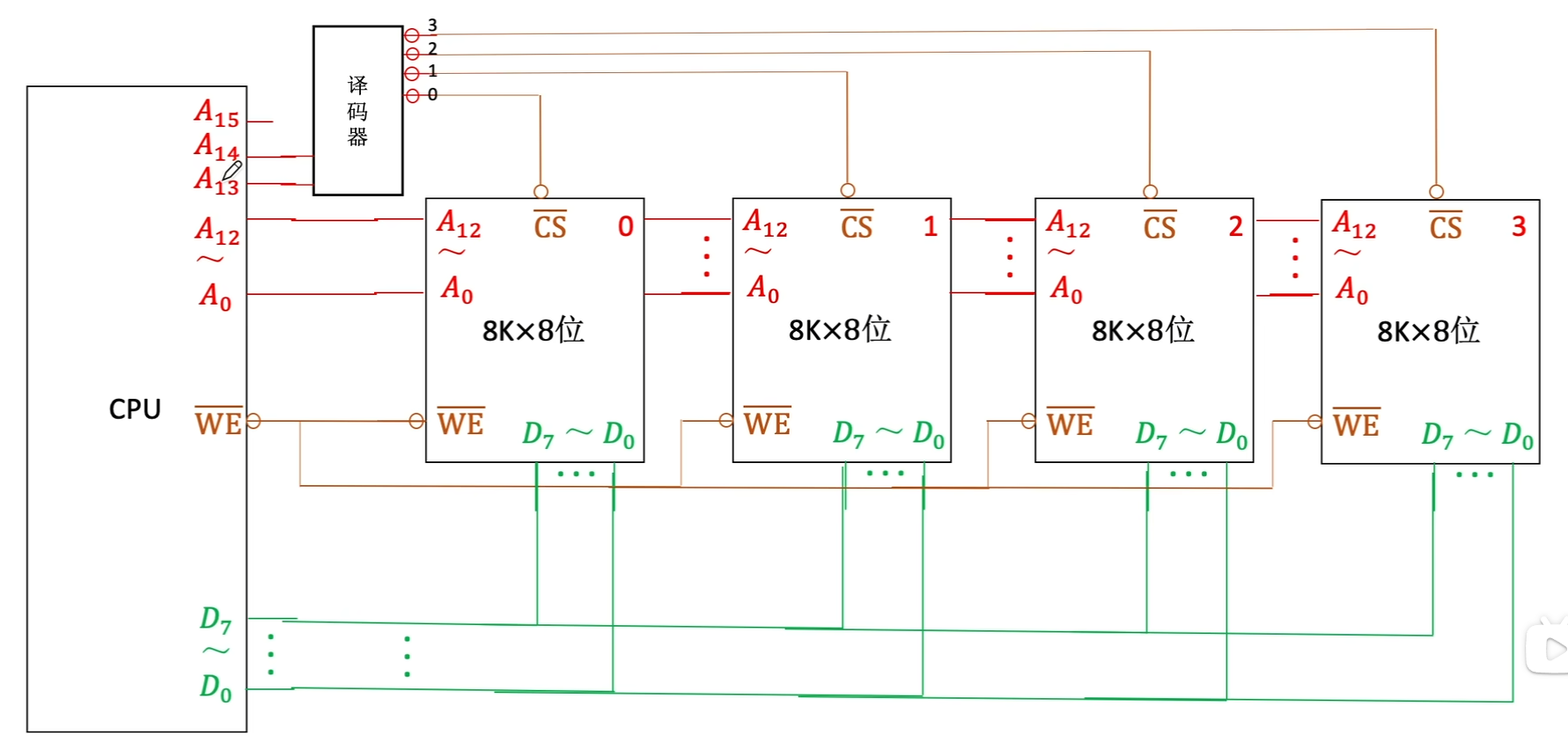

3.6 主存储器与CPU的连接

位拓展:

字拓展:

- 线选法:为每个芯片的片选信号单独分配一个地址总线,电路简单,但是地址空间不连续

- 译码器片选法

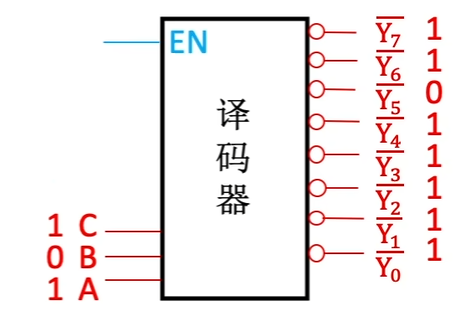

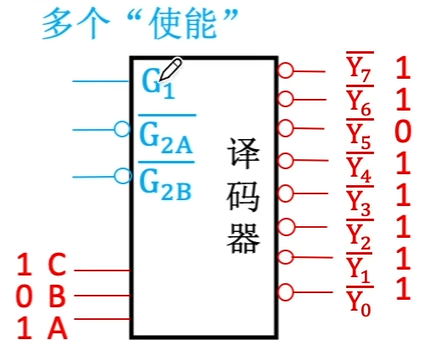

关于译码器的补充:

在有些情况下,比如74ls138芯片,会有多个使能端

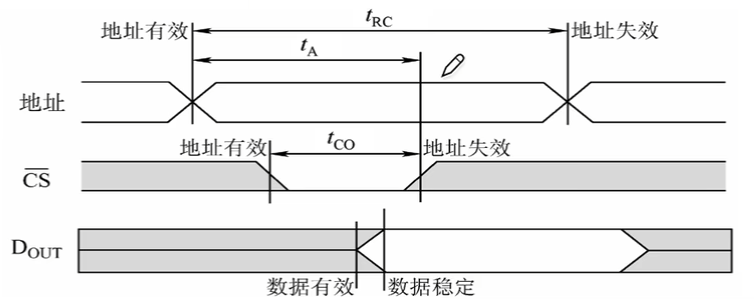

CPU可以通过译码器的使能端控制片选信号的生效时间。先送出地址信号,等电路稳定了,在发出使能信号。

3.7 磁盘

磁盘设备的组成:

- 一块硬盘含有若干个记录面,每个记录面划分为多个磁道,每个磁道又划分为多个扇区(块)。

- 扇区是磁盘读写的最小单位。

- 柱面数:即磁道数目。不同记录面的相同位置的诸磁道构成一个圆柱面。

非格式化容量:磁记录表面可以利用的磁化单元总数。

格式化容量:按照某种特定的记录格式所能存储信息的总量。

所有磁道记录的信息量一定是相同的,而不是圆越大信息越多,故每个磁道的位密度都不同。

平均存取时间 = 寻道时间 + 旋转延迟时间 + 传输时间

磁盘地址的组成:

- 驱动器号

- 柱面号

- 盘面号

- 扇区号

磁盘属于机械式部件,读写操作是串行的,不能在同一时刻既读又写或写两组数据。

廉价冗余磁盘阵列RAID:将多个独立的物理磁盘组成一个独立的逻辑盘,提高安全性,性能和可靠性

- RAID0:没有容错能力

- RAID1:采用两个磁盘同时读写,意味着容量减少一半

- RAID2:采用海明码

3.8 Cache

Cache和主存的映射关系:

全相联映射:主存块可以放在Cache的任意位置

Cache存储空间利用充分,命中率高,但是查找比较慢

直接映射:每个主存块只能映射到Cache的一个特定位置,比如Cache块号 = 主存块号 % Cache总块数

速度最快,但是空间利用率很低,命中率低

组相联映射:Cache块分为若干组,每个主存块可以分到特定分组中的任意位置,组号 = 主存块号 % 分组数

可以看做前面两种方法的折中,综合效果较好

Cache替换算法:

只需要考虑全相联映射和组相联映射

随机算法RAND:若Cache已满,则随机选取一块

命中率低,实际效果很不稳定

先进先出算法FIFO

实现简单,但依旧没考虑局部性原理,容易发生抖动(频繁的换入换出)

近期最少使用LRU

为每个Cache行设置一个计数器,记录每个Cache块已经有多久没被访问了,替换计数器值最大的

最不经常使用LFU

同样,为每个Cache行设置一个计数器,只不过记录每个Cache块被访问了多少次

但是曾经被经常访问的主存块在未来不一定用到,比如微信聊天完成后,其相关Cache块的计数器很高,但是并不会立即被置换出。

Cache写策略:

写命中

写回法:当CPU对Cache写命中时,只修改Cache的内容,只有在此块被换出的时候再写入内存。

全写法:当CPU对Cache写命中时,同时修改Cache和主存(放在写缓冲里)

若写操作过于频繁,可能会因为写缓冲饱和而堵塞

写不命中

- 写分配法:先调入Cache,然后修改Cache的内容(参考写回法)

- 非写分配法:只写入主存,不调入Cache

各级Cache之间常采用全写法和非写分配法,而Cache和主存之间采用写回法和写分配法

四、指令系统

4.1 指令格式

指令字长:一条指令的总长度,可能会变,比如半字长指令、双字长指令

- 定长指令字结构

- 变长指令字结构

指令可以按照操作码长度进行分类

- 定长操作码

- 可变长操作码

按照操作类型分类

- 数据传送,如LOAD

- 算数逻辑操作,即加减乘除与或非

- 移位操作

- 转移指令,如JMP,TRAP

- 输入输出操作,即IO

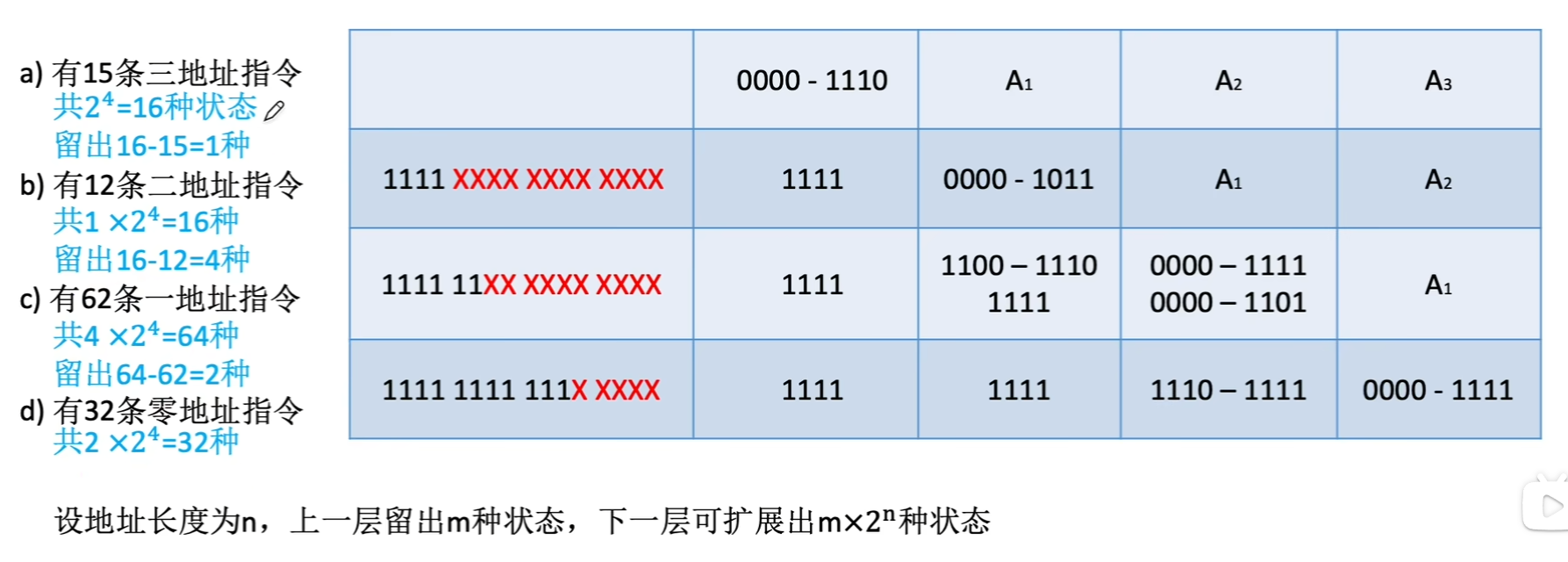

4.2 扩展操作码

什么是扩展操作码:定长指令字结构 + 可变长操作码

对于拓展操作码:

- 优点:在指令长度有限的情况下,能够保持比较丰富的指令种类

- 缺点:增加了译码难度,使控制器的设计复杂化

4.3 指令寻址

CPU如何确定下一条指令的存放地址?

- 顺序寻址:PC = PC + 1个指令字长

- 跳跃寻址:执行转移类指令,如JMP,直接使PC值改变

4.4 数据寻址

- 直接寻址:实现简单,但是寻址范围有限制,且操作数的地址不易修改

- 间接寻址:指令给出的地址是操作数有效地址所在的存储单元,即EA=(A)

- 寄存器寻址:速度快,但是贵

- 寄存器间接寻址:寄存器中的数是操作数主存单元的地址,即EA=(R)

- 隐含寻址:在指令中隐含着操作数的地址

- 立即寻址:即操作数在指令中

- 偏移寻址

- 基址寻址:将基址寄存器BR(即重定位寄存器)的内容加上形式地址,即EA=(BR)+A,便于程序浮动,方便并发

- 变址寻址:与基址寻址相同,只不过使用的是变址寄存器IX,同时IX中存放的是偏移量,这个寄存器是面向用户的,而BR是面向操作系统的。

- 相对寻址:即程序计数器PC的内容作为基地址,形式地址作为偏移,EA=(PC)+"1"+A, 注意,这里的"1"是说明相对下一条指令。

- 堆栈寻址:操作数放在堆栈中,隐含使用堆栈指针SP作为操作数地址

4.5 x86汇编

- 通用寄存器

- eax

- ebx

- ecx

- edx

- 变址寄存器:通常用于处理线性表、字符串

- esi

- edi

- 堆栈基址针ebp

- 堆栈顶指针esp

常见的指令

算数运算:add sub mul imul(有符号数) div idiv neg(取负数) inc dec

对于div和idiv:

div s代表edx:eax/s=eax...edx在x86汇编中,不允许两个操作数都来自主存

逻辑运算:and or not xor shl(逻辑左移) shr(逻辑右移)

其他指令:

- 实现分支结构、循环结构:cmp test jmp

- 实现函数调用:push pop call ret

- 实现数据转移:mov

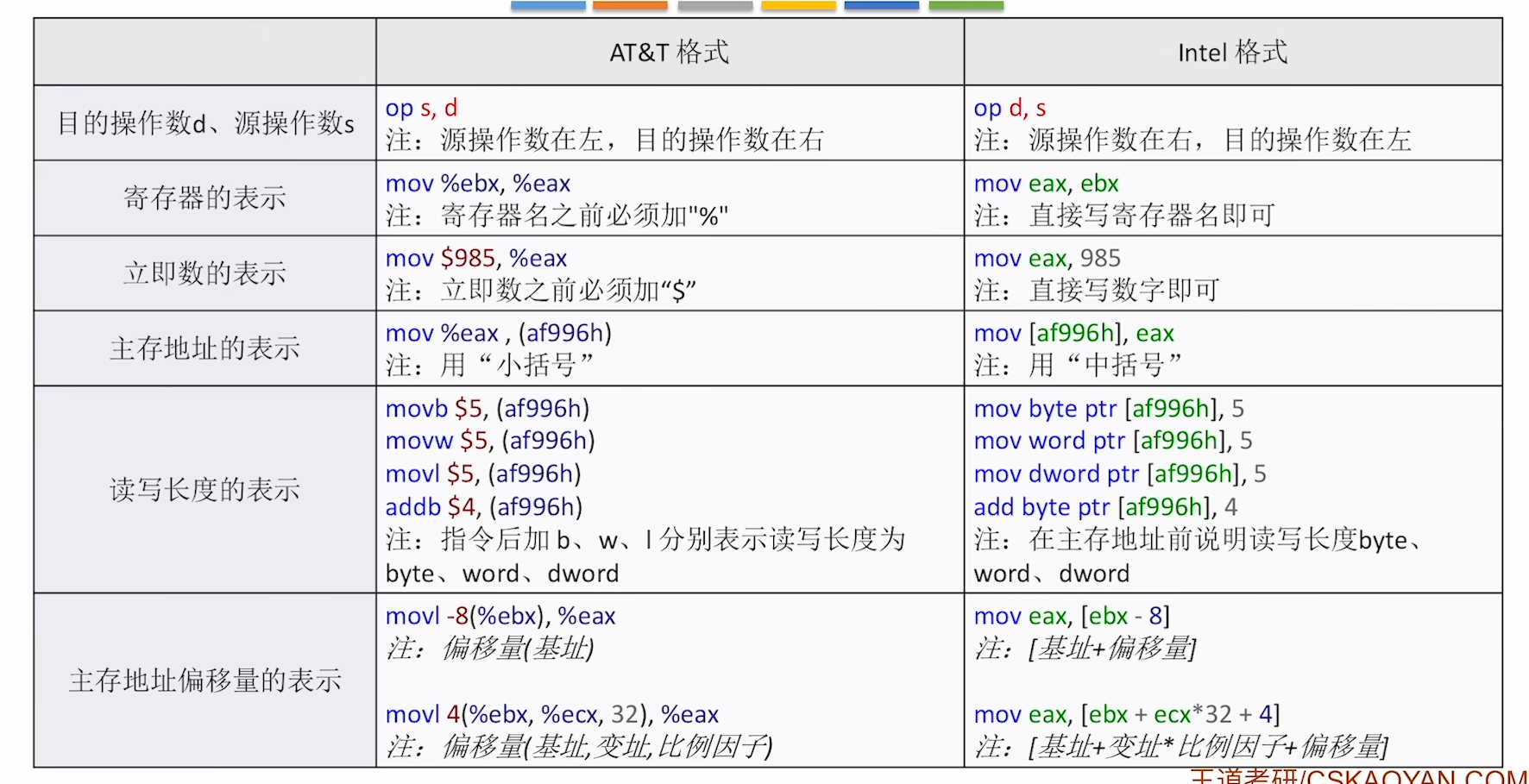

AT&T格式与Intel格式的汇编区别

在Intel x86 处理器中,程序计数器PC通常被称为IP

转移指令:

无条件转移

jmp xxx,其中xxx可以是标号,也可以是地址有条件转移

je:等于时跳转jne: 不等于时跳转jg:大于时跳转jge:大于等于时跳转jl:小于时跳转jle:小于等于时跳转

循环指令:

1 | |

- loop

- loopnz:当ecx!=0 && zf==0 时继续循环

函数调用:

函数调用:call

将IP旧值压栈,设置IP新值(即先push IP,再jmp xxx)

函数返回:ret

将IP值出栈,从而恢复IP寄存器(即pop IP)

ENTER指令:

1

2push ebp

move ebp espLEAVE指令:

1

2mov esp ebp

pop ebp

调用参数:

在函数中,C语言越靠前定义的局部变量越靠近栈顶。参数列表越靠前的参数越靠近栈顶。

因此ebp+8代表第一个参数,ebp+12代表第二个参数。栈帧大小为16B的整数倍,因此可能产生未使用的区域。

4.6 CISC和RISC

CISC:Complex Instruction Set Computer,复杂指令集,如X86架构

- 控制方式:大部分为微程序控制

- 可以通过一定方式实现指令流水线

RISC:Reduced Instruction Set Computer,精简指令集,如ARM架构

- 控制方式:大部分为组合逻辑控制

- 必须实现指令流水线

五、中央处理器

5.1 CPU的功能和结构

数据传输:

- CPU内部单总线方式:结构简单,容易实现,但是性能低,容易出现冲突

- 专用数据通路:结构复杂,不易实现,性能高

- 使用多路选择器进行控制

- 使用三态门进行控制

暂存寄存器:用于暂存从主存读来的数据

5.2 指令周期的数据流

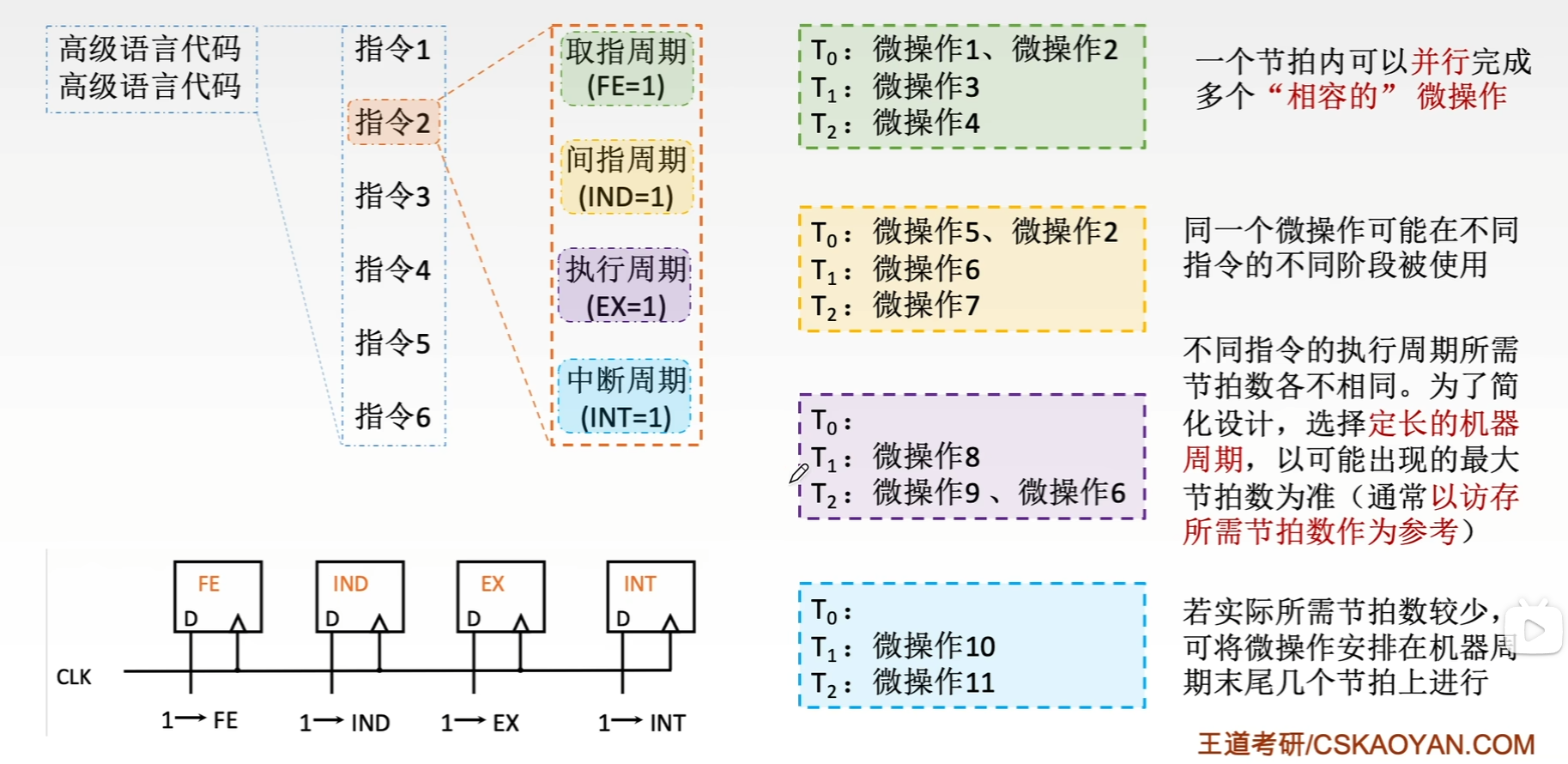

指令周期:CPU从主存中取出并执行一条指令的时间

指令周期由若干机器周期(又称CPU周期)组成。

一个机器周期又包含若干时钟周期(节拍、CPU时钟周期)

每个指令周期可能有不同的机器周期,每个机器周期也可能有不同的节拍。

5.3 控制器的设计

硬布线控制:

CU完成一个微命令(如

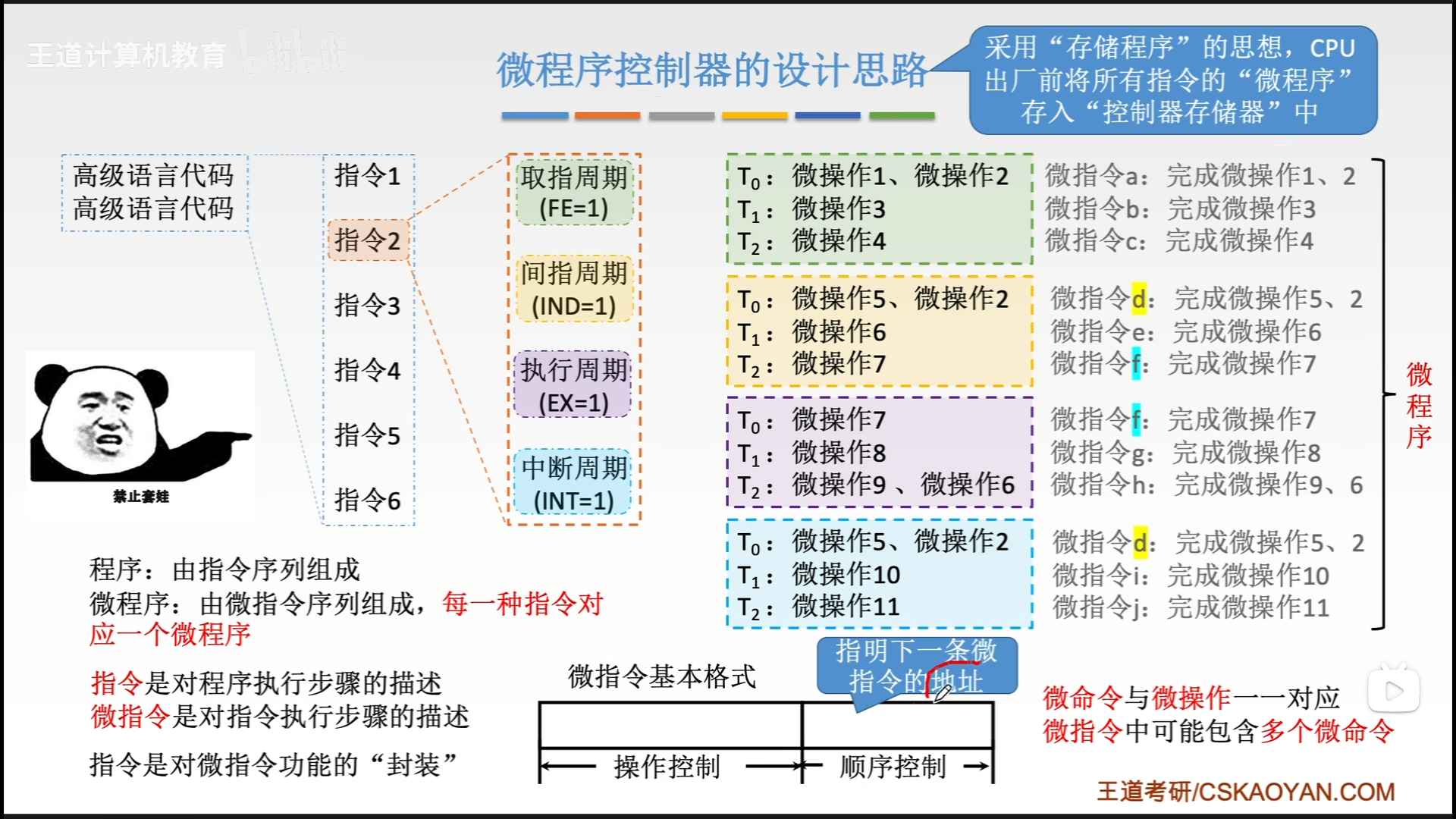

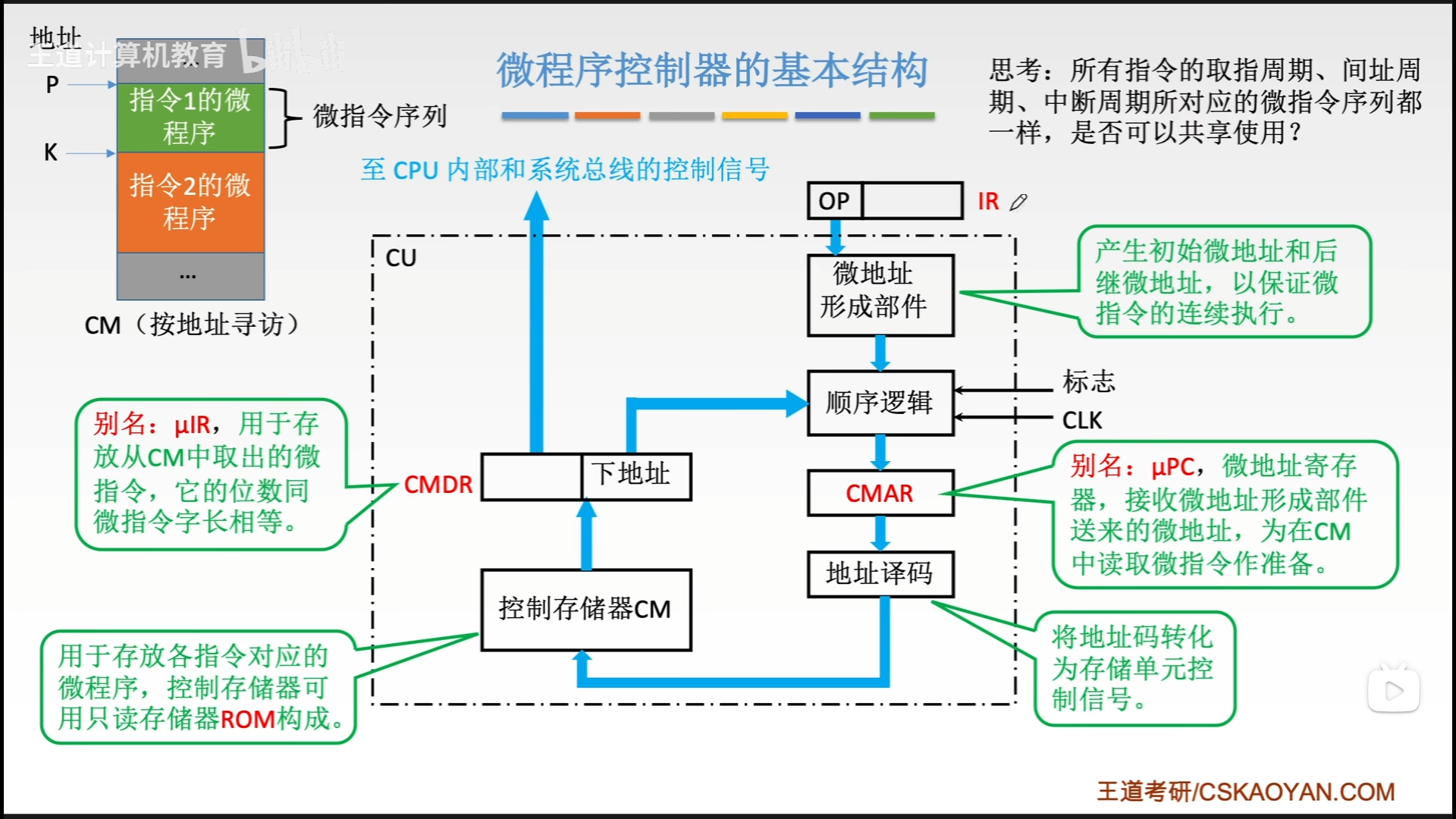

微程序控制:

5.4 指令流水线

六、总线

6.1 总线概述

总线的分类:

- 片内总线

- 系统总线

- 数据总线

- 地址总线

- 控制总线

- 通信总线

系统总线的分类:

- 单总线结构

- 双总线结构

- 三总线结构

七、IO

7.1 IO控制方式

程序查询方式:CPU不断轮询检查IO控制器中的状态寄存器,若状态为已完成,则从数据寄存器中进行读取。

程序中断方式:键盘完成IO之后给CPU发出中断请求

DMA控制方式:DMA接口其实也是一种特殊的IO接口,DMA接口直接与主存连接。每完成一整块数据读写,才发生一次中断。

通道控制方式:通道是一种特殊的处理器,专门处理IO设备

7.2 IO接口

IO接口,又称IO控制器、设备控制器

可以分为两种编制方式:

统一编制

优点:逻辑电路简单,程序设计灵活度高。

缺点:占用主存地址空间,译码速度慢。

独立编制

例如Intel的IN和OUT

优点:使用专门的IO指令,程序编制清晰,可读性好。译码速度快,不占用主存地址空间

缺点:程序设计灵活性差,逻辑电路复杂。

7.3 程序查询方式

独占查询:CPU 100%的时间都在查询IO状态,完全串行

定时查询:在保证数据不丢失的情况下,每隔一段时间就查询一次IO状态。

7.4 中断

中断流程:

- 中断请求

- 中断响应:首先需要检查是否关中断,然后进行中断判优

- 硬件排队器

- 查询程序

- 中断处理

- 中断隐指令:

- 关中断

- 保存断点

- 引出中断服务程序

- 软件查询法

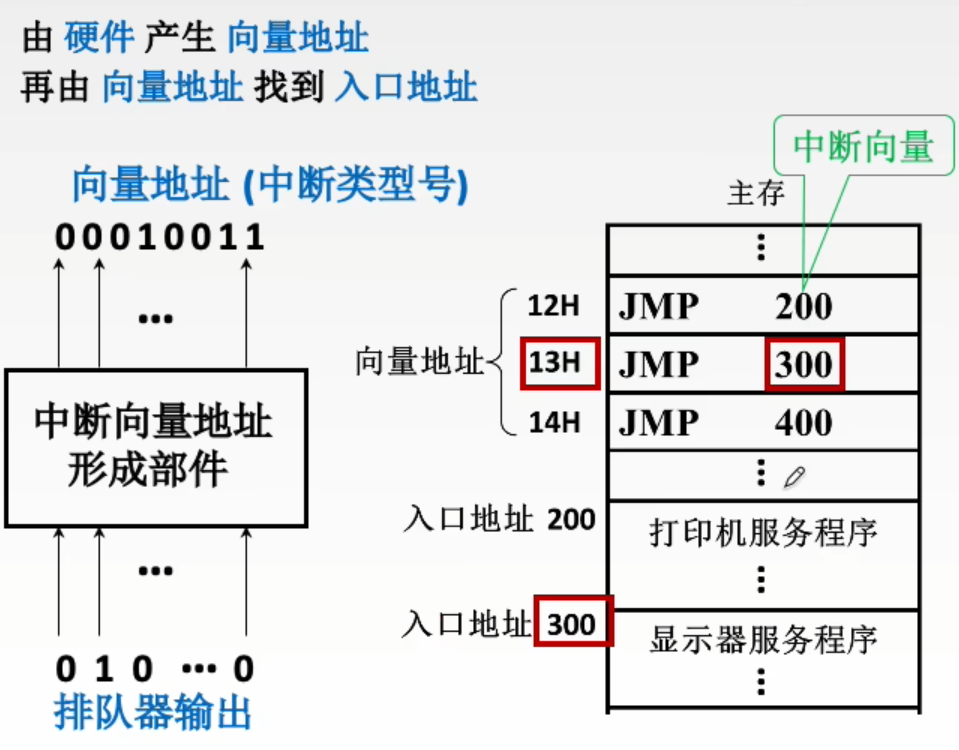

- 硬件向量法

- 中断隐指令:

中断服务程序的主要任务:

- 保护现场

- 中断服务

- 恢复现场

- (开中断)中断返回

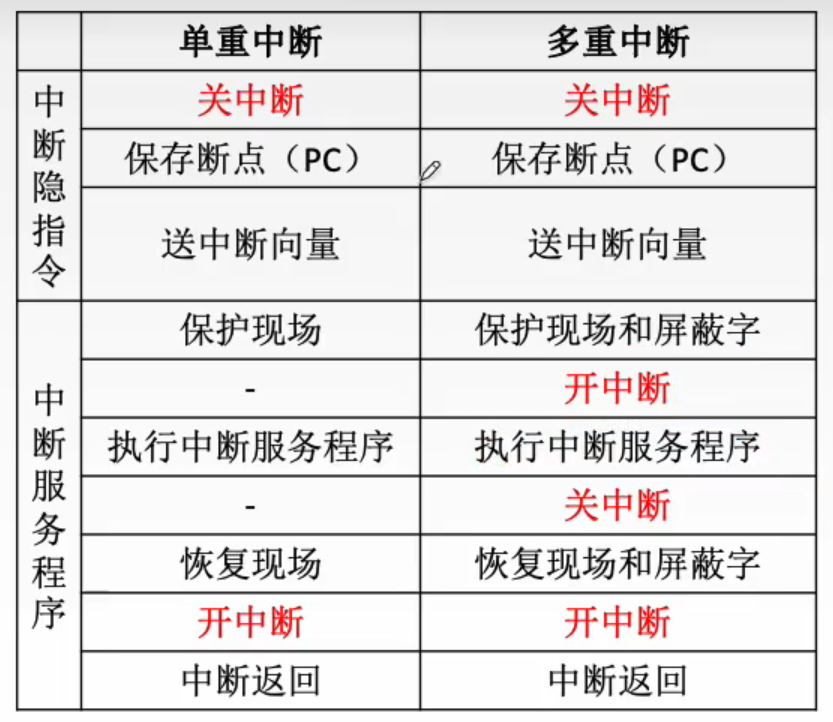

多重中断

中断屏蔽字:若某一个中断对应的位置设置成1,则意味着执行当前中断服务程序的时候,不可以被该中断中断

7.5 DMA方式

主存和DMA控制器之间存在数据通路,但是同时访问主存时可能冲突,有三种方式解决:

停止CPU访问主存

DMA与CPU交替访问主存

周期挪用:

当DMA访存时:

若CPU正在访存:存取周期结束后让出总线

若CPU未访存:DMA访存

若同时访存:DMA优先